- خانه

- رشته کامپیوتر

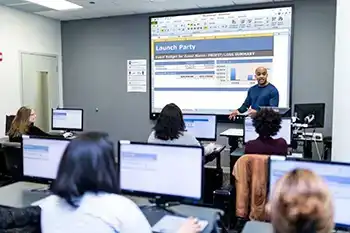

- معرفی رشته مهندسی کامپیوتر

- معرفی رشته علوم کامپیوتر

- معرفی رشته فناوری اطلاعات

- نظر دانشجویان رشته مهندسی کامپیوتر

- درامد رشته کامپیوتر

- مهاجرت رشته کامپیوتر

- شغل های رشته کامپیوتر

- آیا رشته کامپیوتر سخت است؟

- شرایط ورود به رشته کامپیوتر

- رشته کامپیوتر برای دختر

- برای رشته کامپیوتر چه درس هایی باید قوی باشند؟

- زیر شاخه های رشته کامپیوتر (فنی حرفهای و کاردانش)

- معرفی رشته کامپیوتر فنی حرفه ای

- دروس رشته کامپیوتر

- بازار کار رشته کامپیوتر

- آینده رشته کامپیوتر

- بیکاری در رشته مهندسی کامپیوتر

- مزایا و معایب رشته مهندسی کامپیوتر

- رتبه بندی دانشگاه های ایران

- اصطلاحات رشته کامپیوتر به انگلیسی

- آی تی و هر آنچه در مورد آن باید بدانید

- هوش مصنوعی و هر آنچه در مورد آن باید بدانید

- دانلود کتاب های رشته کامپیوتر

- چارت درسی مهندسی کامپیوتر

- ارشد

- کنکور ارشد کامپیوتر

- منابع کنکور ارشد کامپیوتر

- مصاحبه با رتبه های برتر کنکور ارشد کامپیوتر

- فیلم های رایگان کنکور ارشد کامپیوتر

- گرایش های ارشد مهندسی کامپیوتر

- کارنامه های کنکور ارشد کامپیوتر

- دفترچه سوالات کنکور ارشد کامپیوتر

- دروس کنکور ارشد کامپیوتر و ضرایب آن

- تعداد سوالات کنکور ارشد کامپیوتر

- بودجه بندی کنکور ارشد کامپیوتر

- ظرفیت پذیرش کارشناسی ارشد کامپیوتر

- سرفصل دروس کنکور ارشد کامپیوتر

- بهترین دانشگاه های رشته مهندسی کامپیوتر

- معرفی ارشد کامپیوتر

- آزمون آزمایشی کنکور ارشد کامپیوتر

- گرایش های مهندسی کامپیوتر

- کنکور ارشد فناوری اطلاعات

- منابع کنکور ارشد فناوری اطلاعات

- مصاحبه با رتبه های برتر کنکور ارشد فناوری اطلاعات

- فیلم های رایگان کنکور ارشد فناوری اطلاعات

- گرایشهای ارشد فناوری اطلاعات

- کارنامه های کنکور ارشد فناوری اطلاعات

- دفترچه سوالات کنکور ارشد فناوری اطلاعات

- دروس کنکور ارشد فناوری اطلاعات و ضرایب آن

- تعداد سوالات کنکور ارشد فناوری اطلاعات

- بودجه بندی کنکور ارشد فناوری اطلاعات

- ظرفیت پذیرش کارشناسی ارشد فناوری اطلاعات

- معرفی رشته آی تی یا فناوری اطلاعات

- شغل های رشته آی تی

- کنکور ارشد علوم کامپیوتر

- منابع کنکور ارشد علوم کامپیوتر

- مصاحبه با رتبه های برتر کنکور ارشد علوم کامپیوتر

- فیلم های رایگان کنکور ارشد علوم کامپیوتر

- گرایشهای ارشد علوم کامپیوتر

- کارنامه های کنکور ارشد علوم کامپیوتر

- دفترچه سوالات کنکور ارشد علوم کامپیوتر

- دروس کنکور ارشد علوم کامپیوتر و ضرایب آن

- تعداد سوالات کنکور ارشد علوم کامپیوتر

- سرفصل دورس کنکور ارشد علوم کامپیوتر

- بهترین دانشگاه های ایران در رشته علوم کامپیوتر

- علوم کامپیوتر یا مهندسی کامپیوتر

- چارت درسی رشته علوم کامپیوتر

- معرفی رشته علوم کامپیوتر

- مشکلات رشته علوم کامپیوتر

- موارد مشترک کنکور ارشد کامپیوتر، IT و علوم

- مصاحبه با رتبه های برتر کنکور ارشد کامپیوتر، آی تی و علوم کامپیوتر

- معرفی کامل دروس کنکور ارشد کامپیوتر، آی تی و علوم کامپیوتر

- مشاوره از نگاه رتبه های برتر کنکور ارشد کامپیوتر

- دفترچه سوالات کنکور ارشد کامپیوتر، آی تی و علوم کامپیوتر

- تاثیر معدل در کنکور ارشد کامپیوتر، آی تی و علوم کامپیوتر

- ظرفیت پذیرش کارشناسی ارشد کامپیوتر و آی تی

- انتخاب رشته کنکور ارشد کامپیوتر، آی تی و علوم کامپیوتر

- بهترین دانشگاه های ایران

- پلتفرم آزمون و بانک تست کنکور ارشد کامپیوتر، آی تی و علوم کامپیوتر

- پلتفرم برنامهریزی کنکور ارشد کامپیوتر و آی تی

- سامانه تخمین رتبه کنکور ارشد کامپیوترو آی تی

- فیلم آموزشی دروس کنکور کنکور ارشد کامپیوتر، آی تی و علوم کامپیوتر

- کارنامههای کنکور ارشد کامپیوتر و IT

- بودجه بندی سوالات کنکور کنکور ارشد کامپیوتر و آی تی

- کنکور ارشد کامپیوتر

- دکتری

- دروس مهم رشته کامپیوتر

- برنامهریزی کنکور کامپیوتر

- همایشها

- خرید فیلمها

- دورههای مهارتی

- بلاگ

- دیگر خدمات

- پلتفرم آزمون و بانک تست

- پلتفرم برنامهریزی

محبوبترینها : برنامه نویسی علم داده رشته کامپیوتر کنکور شبکه و امنیت هوش مصنوعی ساختمان داده منطقی

0

ورود | ثبت نام